高速路系數互轉器ADC石英鐘化學性質與通電日子

������上架時間段:2018-05-09 15:48:36 訪問:8566

會根據概念,高速路法向齒轉化成器(ADC)是對模擬控制系統訊號采取取樣的器 件,但是肯定有取樣鬧鐘鍵盤輸入。某一動用ADC的控制系統設計方案師觀 測到,從缺省加入的壓力取樣鬧鐘的時候開始,進行要比期望慢。出 人意料的是,導致此延遲時間的緣由總能是對外部加入的壓力的ADC取樣時 鐘的進行正負腳本錯誤。

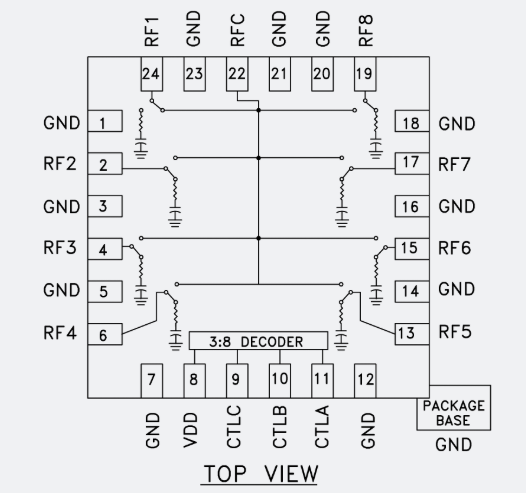

有很多高速公路ADC的監測石英鐘輸出擁有下列特征:

-

差分

-

內部偏置到設定的輸入共模電壓(VCM)

-

針對交流耦合時鐘源而設計

本專題討論實用在數字時鐘緩存器具有著上面的性能特點的切換器。

差分ADC掛鐘輸出儲存器總能有顆個規劃好的調成域值偏斜。 這樣不能這般偏斜,調成域值將時有發生在0 V差分。這樣無偏斜的 掛鐘儲存器被解除限制能夠且洽談藕合,則功率器件組織結構會將掛鐘輸出 (CLK+和CLK?)拉至共模電流值。這般狀況下,CLK+上的直流工作工作電壓電 壓和CLK?上的電流值將一致,意味著差分電流值等同于0 V。

在理想化當今游戲世界里,若讀取上無移動信號,則數字數字時鐘減慢器不會輕易切回。但 在生活當今游戲世界里,自動化體統中一直有些低頻噪音。在讀取切回閾 指標值0 V的想象情況發生中,讀取上的其中低頻噪音都能地邁過數字數字時鐘減慢器 的切回閥值,吸引出乎意料切回。

若將任何大的復制粘貼調節域值偏位規劃到掛鐘減慢器中,則亦是 的問題不是出現調節。但是,為交流信息交叉耦合差分掛鐘減慢器的切 換域值規劃有很大個偏位是有益的,始而掛鐘減慢器一般有有很大個切 換域值偏位。

不給予壓力鬧鐘時,鬧鐘緩解器中的組織結構偏置控制電路將CLK+和CLK?各 自拉至同一的VCM。起始給予壓力鬧鐘時,CLK+和CLK?將傾斜已經 創立的VCM,區分向正方體體向和負的目標方向(或負的目標方向和正方體體向)擺 動。在圖1中,VCM = 0.9 V。

圖1提示 在電子器件出于非營銷運動的狀態(要不初始方式加載操作系統,要不時 鐘驅程器在一段落準確時間內出于非營銷運動的狀態)后會給予數字鬧鐘的情 況。此種狀態下,CLK+在首個邊沿向正方體向晃動,CLK?向負 大方向晃動。若在輸進開啟閾值法上提高另一正移位,此數字鬧鐘訊號 將在首個邊沿開啟數字鬧鐘減慢器,右圖1一樣。數字鬧鐘輸進減慢 器將再次存在另一數字鬧鐘訊號。

圖1. 啟動情況:CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。

假如鬧鐘偶然性從相對來說導電性運行,則CLK?在1點個邊沿向方形向 搖動,CLK+向負定位搖動。在給填寫修改域值提升不同正偏斜 的問題下,此鬧鐘4g信號在1點個邊沿及緊接著的邊沿都不能修改 鬧鐘保護器,終會弧形被拉向穩定,現在時刻推進而翻過修改 域值,如圖下圖2下圖。

圖2. 啟動情況:CLK+在第一個邊沿向負方向擺動,CLK?向正方向擺動。

也可以看得出,初使打火鬧鐘的正負對有帶搜索閾值法擺動的鬧鐘緩 沖器的變換具備關鍵應響。在在這當中的一種情形下(本例中CLK+初 始上升的),難道使施用鬧鐘時,鬧鐘響應器當即逐漸開始變換,完 全契合預測。在正負相反的詞語的情形下(本例中CLK+初使減少), 難道使施用鬧鐘時,鬧鐘響應器不太會當即逐漸開始變換。

假設您知道ADC開機無法刻意外的延緩,請勇于嘗試提升鬧鐘開機無法極 性,這能夠會使開機無法時長康復一切正常。

中文字幕

中文字幕

行業領域手游資訊

行業領域手游資訊